Интерфейс JESD204 в теории и на практике

Введение

На протяжении последних лет наиболее популярными интерфейсами АЦП/ЦАП были CMOS и LVDS. Постепенно требования, предъявляемые отраслью, возрастали. И соответственно, компании-производители начали работать над новыми АЦП и ЦАП с все более высокими скоростью преобразования и динамическим диапазоном. Очевидной стала потребность в более эффективных интерфейсах: чтобы идти в ногу с непрерывно повышающейся частотой дискретизации преобразователей, в новых проектах следовало использовать более быстрый по сравнению с CMOS или LVDS интерфейс и более эффективный с точки зрения таких параметров, как потребление и количество выводов.

В результате несколько лет назад комитет по стандартам JEDEC выпустил первую спецификацию JESD204. По сравнению с CMOS или LVDS JESD204 самым очевидным преимуществом является максимальная скорость передачи данных. Кроме того, JESD204 позволяет уменьшить количество используемых выводов, что приводит к сокращению размеров корпусов и меньшему количеству линий, которые надо развести на плате, а это, в свою очередь, значительно снижает сложность платы и положительно влияет на стоимость изготовления.

Надо отметить, что стандарт JESD изначально спроектирован масштабируемым, а значит, со временем он будет адаптироваться, чтобы соответствовать дальнейшим вызовам. Это можно проиллюстрировать теми изменениями, которые стандарт уже претерпел: с момента релиза в 2006 году было выпущено четыре ревизии, и в настоящий момент действует самая последняя ревизия — С. Поскольку постепенно стандарт принимался все большим количеством компаний — производителей преобразователей данных, (и, соответственно, компаний, выпускающих ПЛИС), он постепенно усовершенствовался и получал новые функции, повысившие эффективность и простоту реализации. Стандарт применяется как в аналого-цифровых (АЦП), так и в цифро-аналоговых преобразователях (ЦАП), и в первую очередь предназначен для использования как общий стандартный интерфейс для ПЛИС (хотя может взаимодействовать и с ASIC).

Что такое JESD и что о нем нужно знать?

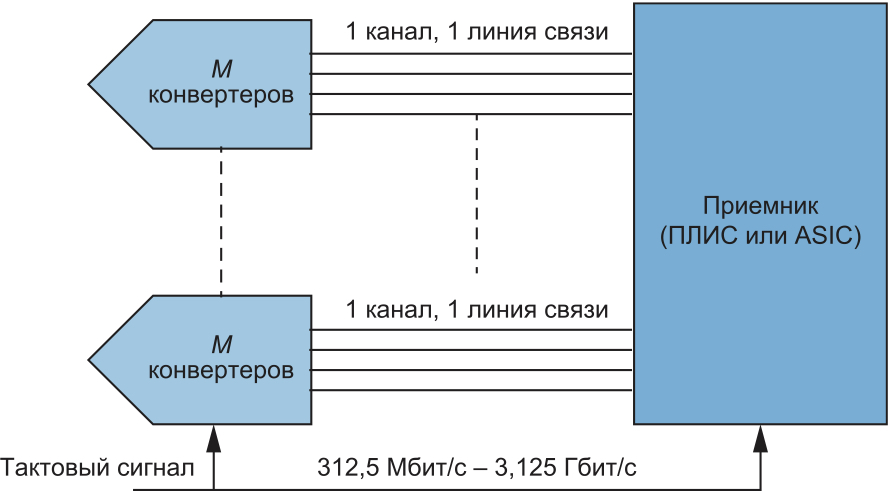

В апреле 2006 года была принята оригинальная версия стандарта JESD204. Стандарт описывал гигабитный последовательный обмен данными между преобразователем и приемником, в качестве которого обычно выступает FPGA или ASIC. В этой версии JESD204 последовательный канал передачи данных был определен для одной последовательной линии связи между одним или несколькими преобразователями и одним приемником. Схематичное представление дано на рис. 1.

Показанная линия — это физический интерфейс между М преобразователей и приемником, который состоит из дифференциальной пары, использующей драйверы и приемники на токопереключательной логике (CML). Представленное соединение является последовательным каналом передачи данных между преобразователями и приемником. Глобальная линия тактирования приходит как на преобразователь, так и на приемник и обеспечивает синхронизацию канала JESD204 между устройствами.

Скорость передачи данных по одной линии определена стандартом в пределах 312,5 Мбит/с — 3,125 Гбит/с, импеданс источника и приемника сигнала в пределах 100 Ом ±20%. Номинальный уровень дифференциального напряжения 800 мВ с диапазоном синфазного напряжения 0,72–1,23 В. В линии связи предусмотрено кодирование 8b/10b, которое содержит встроенное тактирование, что позволяет избежать использования в разводке дополнительного тактового сигнала и сопутствующих сложностей с его выравниванием относительно передаваемых данных на высоких скоростях. По мере того как стандарт JESD204 набирал популярность, возникла необходимость в его пересмотре, чтобы включить поддержку нескольких выровненных последовательных линий с несколькими конвертерами и, таким образом, учесть растущие скорости и разрешения преобразователей.

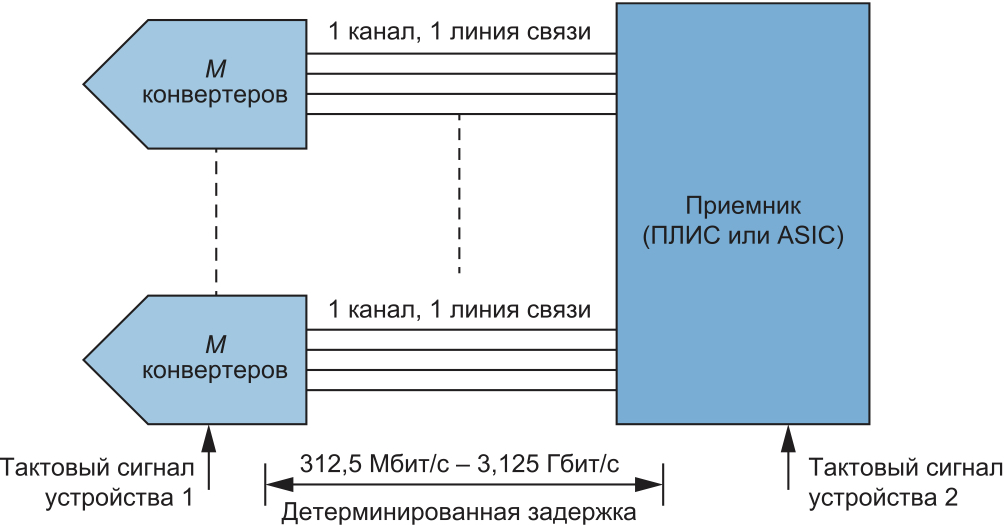

Это привело к выпуску первой ревизии стандарта JED204, сейчас известная как JESD204A. В ней добавлена возможность поддержки подключения нескольких преобразователей с помощью нескольких выровненных последовательных линий. Скорость передачи данных 312,5 Мбит/с — 3,125 Гбит/с осталась неизменной, как и тактовая частота и электрическая спецификация интерфейса. Расширение возможностей стандарта по поддержке нескольких выровненных последовательных линий позволило обеспечить поддержку максимальной скорости передачи данных 3,125 Гбит / с для преобразователей с высокой частотой дискретизации и высоким разрешением. На рис. 2 показано графическое представление дополнительных возможностей, добавленных в ревизии JESD204A для поддержки нескольких линий.

Хотя исходный стандарт JESD204 и пересмотренный стандарт JESD204A имели более высокую производительность, чем предыдущие интерфейсы, им все еще не хватало одного ключевого элемента. Этим недостающим элементом является детерминированная задержка в сериализованных данных в канале передаче данных. При работе с преобразователем важно знать временное соотношение между дискретизированным сигналом и его цифровым представлением, чтобы правильно воссоздавать дискретизированный сигнал в аналоговой области после получения сигнала (эта ситуация, конечно, для АЦП, аналогичная ситуация верна и для ЦАП). На это временное соотношение влияет задержка преобразователя, которая для АЦП определяется как число тактов между моментом непосредственного старта дискретизации входного сигнала и моментом, когда его цифровое представление появляется на выходах преобразователя. Аналогичным образом в ЦАП задержка определяется как количество тактов между временем, в течение которого цифровой сигнал защелкивается на входе ЦАП, и временем, когда состояние аналогового выхода не начнет изменяться. В стандартах JESD204 и JESD204A не было определенных возможностей, которые бы устанавливали детерминированную задержку преобразователя и его сериализованных цифровых входов/выходов. Кроме того, продолжали увеличиваться скорости и разрешение преобразователей. Эти факторы привели ко второй ревизии стандарта — JESD204B.

Стандарт JESD204B

Вторая и на данный момент наиболее используемая (хотя ревизия JESD204C уже поддерживается самыми современными конвертерами), ревизия JESD204B была выпущена в июле 2011 года. Одним из ключевых положений пересмотренного стандарта стало добавление возможностей достижения детерминированной задержки. Кроме того, поддерживаемые скорости передачи данных были доведены до 12,5 Гбит/с с разбивкой по различным классам скорости устройств. Эта версия стандарта требует перехода от использования тактовых импульсов от одного внешнего источника тактирования к непосредственному тактированию каждого устройства. На рис. 3 показаны дополнительные возможности, добавленные в ревизию JESD204B.

В двух предыдущих ревизиях стандарта JESD204 не были определены положения, обеспечивающие детерминированную задержку интерфейса. Редакция JESD204B устраняет эту проблему, предоставляя механизм, обеспечивающий повторяемую и детерминированную задержку в промежутках между циклами подачи питания и ресинхронизации канала передачи данных. В качестве одного из подходов для достижения этого использован запуск инициализирующей выравнивающей последовательности между преобразователями одновременно по всем линиям в четко определенный момент времени по входному сигналу SYNC~. Другая реализация заключается в применении сигнала SYSREF (сигнал является нововведением и определен для стандарта JESD204B). Сигнал SYSREF действует как эталон синхронизации, устанавливает и выравнивает внутренние делители частоты тактовых сигналов устройства, а также локальные схемы тактирования в каждом передатчике и приемнике. Это помогает обеспечить в системе детерминированную задержку. Спецификация JESD204B поддерживает три подкласса устройств: подкласс 0 — нет поддержки детерминированной задержки; подкласс 1 — детерминированная задержка с использованием SYSREF; подкласс 2 — детерминированная задержка с использованием SYNC~. По сути, подкласс 0 ничем не отличается JESD204A. Подкласс 1 в первую очередь предназначен для преобразователей, имеющих скорость 500 MSPS и выше, в то время как подкласс 2 предусмотрен главным образом для преобразователей, работающих со скоростью ниже 500 MSPS.

В дополнение к детерминированной задержке версия JESD204B поддерживает более высокие скорости передачи данных (до 12,5 Гбит/с), а устройства делятся на три различных класса поддерживаемой скорости. Импеданс источника и приемника одинаков для всех трех скоростей и определяется как 100 Ом ±20%. Первый класс соответствует скоростям передачи данных из версий стандарта JESD204 и JESD204A и определяет скорость передачи данных через интерфейс до 3,125 Гбит/с. Второй класс определяет скорость передачи данных через интерфейс до 6,375 Гбит/с. Для второго класса минимальный уровень дифференциального напряжения снижается до 400 мВ в размахе, по сравнению с 500 мВ в размахе у первого класса скорости. Третий класс определяет скорость передачи данных через интерфейс до 12,5 Гбит/с. Для него минимальный уровень дифференциального напряжения снижен до 360 мВ в размахе. По мере того как скорости передачи данных растут, минимальный необходимый уровень дифференциального напряжения уменьшается, чтобы упростить физическую реализацию за счет снижения требуемых скоростей переключения фронтов в выходных драйверах.

Для обеспечения большей гибкости в ревизии JESD204B перешли с общей синхронизации на тактирование каждого устройства в отдельности. Ранее в версиях JESD204 и JESD204A внешние тактовые сигналы были абсолютным эталоном синхронизации в системе JESD204. Это не предполагало высокой гибкости и усложняло проектирование системы, поскольку следовало распределить один и тот же синхросигнал на несколько устройств и учесть возможные задержки по пути его прохождения. В JESD204B привязка к времени для каждого из устройств — его внутренний источник синхросигнала. Каждый преобразователь и источник получает собственный синхросигнал от схемы генератора, которая выдает синхросигнал на всех устройствах, опираясь на общий для всех источников импульсов (например, кварцевый генератор или резонатор). Это обеспечивает большую гибкость при проектировании системы, но требует, чтобы для данного устройства было четко задано соотношение между входной частотой источника и тактовым генератором устройства.

Стандарт JESD204C

Последняя на сегодня ревизия JESD204C является и самой сложной с технической точки зрения. Подробно мы поговорим о ее особенностях и рассмотрим на практике, как подключить конвертер Analog Devices cJESD204C к ПЛИС Arria 10GX, в следующей статье, посвященной интерфейсу JESD204. Пока ревизия С не имеет широкого распространения, и количество преобразователей, поддерживающих JESD204C, невелико. Поэтому здесь перечислим только основные отличия от ревизии B.

Прежде всего, изменения коснулись максимальной скорости — 32 Гбит/с против 12,5 у JESD204B. Поскольку на скоростях выше 16 Гбит/с не рекомендовано использовать кодирование 8b/10b, в спецификацию JESD204C добавлена поддержка 64-битного кодирования 64b/66b (IEEE 802.3). Также был включен механизм FEC(Forward Error Correction), который поддерживается при использовании 64-битного кодирования и может быть очень полезен в задачах, требующих прецизионной точности в преобразовании.

JESD против LVDS

Подобно тому как несколько лет назад LVDS начал обгонять CMOS в качестве технологии выходных драйверов цифрового интерфейса преобразователей, в ближайшие несколько лет по тому же пути пойдет и JESD204. Хотя, как технология, CMOS все еще применяется сегодня, но в большинстве приложений LVDS уже сменил ее. Скорость и разрешение преобразователей, а также стремление к снижению мощности в итоге делают CMOS и LVDS неоптимальными. По мере увеличения скорости передачи данных токи переключения на выходах CMOS-драйверов растут, что приводит к более высокому энергопотреблению. Хотя для LVDS ток и, следовательно, энергопотребление остается относительно неизменным в процессе функционирования, этот интерфейс имеет ограничение по максимальной поддерживаемой скорости.

Это связано с архитектурой драйвера и с многочисленными линиями данных, которые должны быть синхронизированы с тактовым сигналом. На рис. 4 показаны различные требования к потребляемой мощности выходов CMOS, LVDS и CML для двойного 14-разрядного АЦП.

Драйверы CML, на которых физически базируется интерфейс JESD, становятся более эффективными с точки зрения энергопотребления, когда скорость преобразователя превышает приблизительно 150–200 MSPS, а разрешение больше 14 бит. Преимущество CML состоит в том, что для данного разрешения требуется меньше выходных пар, чем в драйверах LVDS и CMOS, благодаря сериализации данных. Дополнительное преимущество драйверов CML, использующихся в интерфейсе JESD204B, в том, что спецификация требует снижения пиковых уровней напряжения по мере увеличения частоты дискретизации и увеличения скорости выходной линии.

Количество выводов, необходимых для одного и того же разрешения и частоты дискретизации преобразователя, также значительно меньше. В таблице 1 приведено количество выводов для трех различных интерфейсов для преобразователя с частотой дискретизации 200 MSPS с разным числом каналов и разрешением. Так, для данных каждого канала в случае CMOS и LVDS предусмотрена синхронизация тактового сигнала и максимальная скорость 4 Гбит/с для передачи данных в случае JESD204B с использованием CML. Причины перехода к JESD204B с применением CML становятся очевидными, если взглянуть на эту таблицу и увидеть, насколько значительное сокращение количества выводов может быть достигнуто.

|

Количество каналов |

Разрешение, бит |

Количество выводов CMOS |

Количество выводов LVDS (DDR) |

Количество выводов CML(JESD204B) |

|

1 |

12 |

13 |

14 |

2 |

|

2 |

12 |

26 |

28 |

4 |

|

4 |

12 |

52 |

56 |

8 |

|

8 |

12 |

104 |

112 |

16 |

|

1 |

14 |

15 |

16 |

2 |

|

2 |

14 |

30 |

32 |

4 |

|

4 |

14 |

60 |

64 |

8 |

|

8 |

14 |

120 |

128 |

16 |

|

1 |

16 |

17 |

18 |

2 |

|

2 |

16 |

34 |

36 |

4 |

|

4 |

16 |

68 |

72 |

8 |

|

8 |

16 |

136 |

144 |

16 |

Острые проблемы, связанные с JESD204B

При реализации интерфейса JESD204B было необходимо идти на компромисс между всеми его преимуществами и имеющимися сложностями и тонкостями работы, которые отличают его от существовавших на тот момент форматов интерфейсов и протоколов. Как и в случае с любым стандартом, очевидно следующее: чтобы завоевать популярность у разработчиков и стать для них более привлекательным, чем распространенные CMOS или LVDS, новый интерфейс должен функционировать безотказно. Хотя стандарт JESD204B хорошо документирован JEDEC, некоторая специфическая информация о нем требует объяснения или изучения в дополнительных источниках. А потому весьма полезно иметь под рукой краткое руководство с описанием стандарта, принципов его работы и методов решения проблем, если таковые возникнут.

В этом разделе речь пойдет о том, как построить интерфейс между АЦП и ПЛИС с помощью JESD204B и определить, что он работает правильно, а главное, как устранить неполадку, если возник какой-то сбой. Предлагаемые методы диагностики предусматривают использование общедоступного испытательного и измерительного оборудования, включая осциллографы, логические анализаторы и программные инструменты, такие как SignalTap от Intel FPGA®. Мы разберем сигналы, которыми оперирует интерфейс, чтобы дать представление о разных подходах к визуализации сигналов.

Интерфейс JESD204B использует три фазы для установки синхронизированного канала передачи данных: синхронизация кодовой группы (CGS), начальная синхронизация полосы (ILAS) и фаза передачи данных. Требуемыми сигналами для передачи являются общий опорный тактовый сигнал (тактовый сигнал устройства), по меньшей мере одно дифференциальное электрическое CML-соединение для физической передачи данных (называемое линией данных — lane) и хотя бы один сигнал синхронизации (SYNC~ и, возможно, SYSREF). Используемые сигналы зависят от подкласса:

- 0 — тактовый сигнал устройства, линия данных и SYNC~;

- 1 — тактовый сигнал устройства, линия данных, SYNC~ и SYSREF;

- 2 — тактовый сигнал устройства, линия данных и SYNC~.

Во многих случаях подкласс 0 оптимален, поэтому на нем мы и сфокусируемся, чтобы проиллюстрировать подходы к решению проблем. Надо понимать, что подкласс 1 и подкласс 2 предоставляют методы для установления детерминированной задержки. Это важно в приложениях, где требуется синхронизация нескольких устройств, системная синхронизация или фиксированная задержка (например, когда системе нужен известный фронт для начала выборки или необходима реакция на входной сигнал в течение заданного времени).

На рис. 5 показана упрощенная линия связи JESD204B от передающего устройства (АЦП) к приемному устройству (ПЛИС), причем данные от одного АЦП проходят по одной линии данных. Хотя в спецификации JESD204B есть много разных параметров, некоторые из них имеют особое значение именно для установления связи. Ключевые переменные из спецификации (обратите внимание, что эти значения обычно представлены как X–1):

- M — число преобразователей;

- L — число физических линий;

- F — количество октетов в фрейме;

- K — количество фреймов в мультифрейме;

- N и N’ — разрешение преобразователя и количество разрядов (бит) на выборку (кратно 4), соответственно. N’ — то же, что N + контрольный и пустой бит.

Подкласс 0: этапы синхронизации

Как отмечено выше, многие приложения могут использовать относительно простой режим работы подкласса 0. Это также самый простой режим в плане установки и проверки канала связи. Подкласс 0 использует три фазы для установления и мониторинга синхронизации: фаза CGS, фаза ILAS и фаза данных.

Рис. 6. Состояние выходов JESD204B подкласса 0 в течение фазы CGS (два канала, одна ПЛИС с двумя АЦП)

На рис. 6 и 7показана каждая фаза с данными, представленными в разных форматах — точно так, как их можно увидеть на осциллографе, логическом анализаторе или виртуальном анализаторе ввода/вывода FPGA, например Altera SignalTap.

Рис. 7. Состояние логических выходов при передаче символов K28.5 и распространение сигнала по тракту JESD204B Tx

Фаза синхронизации кодовой группы — CGS

Наиболее значимые этапы фазы CGS, которые можно проследить на линии связи, показаны на рис. 2, где они соответственно отмечены пятью точками.

- приемник выдает запрос на синхронизацию, установив низкий уровень сигнала SYNC~.

- приемопередатчик передает символы, колированные K5 (10 бит/символ), декодированные началом каждого следующего символа;

- приемник подтверждает синхронизацию, когда без ошибок принято как минимум четыре последовательных K5-символа. После этого приемник поднимает сигнал SYNC~;

- приемник должен принять минимум четыре 8-B/10-B символа без ошибок, иначе синхронизация считается несостоявшейся и канал остается в фазе синхронизации кодовой группы;

- фаза синхронизации кодовой группы заканчивается и начинается фаза ILAS — начальная синхронизация полосы.

Символ K28.5, также известный как K-символ, в стандарте JESD204B можно отобразить, это показано на рис. 3. Стандарт требует действующей нейтральной нечетности. Кодирование 8 B/10 B допускает сбалансированную последовательность, которая в среднем содержит равное количество единиц и нулей. Каждый символ 8 B/10 B может иметь положительную (больше единиц) или отрицательную (больше нулей) нечетность, а четность текущего символа определяется текущей суммой предыдущих отправленных символов. Обычно это достигается поочередной передачей слова с положительной четностью, за которым следует слово отрицательной четности. На рис. 6 показаны обе полярности символа K28.5.

Обратите внимание на следующие ключевые моменты:

- последовательное значение представляет логические уровни 10 битов, передаваемых по полосе, в том же виде, как можно увидеть на осциллографе, при измерении сигналов на физическом интерфейсе;

- 8 B/10 B представляет логические значения (10 бит), передаваемые по полосе, как это можно видеть с помощью логического анализатора, подключенного к физическому интерфейсу;

- Значение данных и логический сигнал данных представляют логические уровни символа внутри блока приемопередатчика JESD204B до кодирования B/10 B, как можно увидеть с помощью инструментов логического анализа FPGA, в частности Xilinx ChipScope или Altera SignalTap;

- символ отображает шестнадцатеричное значение символа на физическом уровне, который должен быть передан, с учетом четности;

- знак (Character) обозначает символ на уровне протокола JESD204B, как указано в спецификации JEDEC.

Фаза начальной синхронизации полосы — ILAS

На этапе ILAS появляются четыре мультифрейма, которые позволяют приемнику выравнивать линии данных по всем каналам и верифицировать параметры тракта передачи данных. Выравнивание требуется для компенсации разницы в длине проводников и любых разбеганий в приеме символов, которые вводят приемники. Каждый последующий мультифрейм из четырех следует сразу за предыдущим (рис. 4). Независимо оттого, включен ли параметр кодирования канала, ILAS всегда передается без кодирования.

Фаза ILAS начинается после сброса сигнала SYNC~ (устанавливается в «лог. 1»). После того как передатчик отследил (внутри АЦП) полный мультифрейм, он начнет передавать четыре мультифрейма. Между необходимыми символами вставляются пустые фрагменты (фиктивные части выборки АЦП), так что передаются полные мультифреймы (рис. 4). Четыре мультифрейма представляют собой следующее:

- мультифрейм 1: начинается с K0 — символа /R/ и заканчивается K28.0 — символом /A/;

- мультифрейм 2: начинается с символа /R/, после которого идет K4 — символ /Q/. После этого идут параметры конфигурации — 14 октетов данных (табл. 2). Заканчивается символом /A/;

- мультифрейм 3: то же, что мультифрейм 1;

- мультифрейм 4: то же, что мультифрейм

Длина фрейма может быть рассчитана для параметров JESD204B:

S × (1/частота дискретизации),

то есть

(количество выборок/преобразователь/фрейм) × (1/частота дискретизации).

Например, преобразователь, работающий со скоростью 250 MSPS, который имеет одну выборку на преобразователь на фрейм (в этом случае S равно 0, поскольку он закодирован как двоичное значение — 1), имеет фрейм длиной 4 нс:

1 × (1/250 МГц) = 4 нс.

Длина мультифрейма может быть рассчитана для параметров JESD204B:

К × S × (1/частота дискретизации),

то есть

(количество выборок/преобразователь/фрейм) × (количество фреймов/мультифрейм) × (1/частота дискретизации).

Например, преобразователь, работающий со скоростью 250 MSPS, который имеет одну выборку на конвертер на фрейм и 32 фрейма на мультифрейм, имеет мультифрейм длиной 128 нс:

1 × 32 × (1/250 МГц) = 128 нс.

|

№ Octet |

Bit 7 (MSB) |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 (LSB) |

|

0 |

DID[7:0] |

|||||||

|

1 |

ADJCNT[3:0] |

BID[3:0] |

||||||

|

2 |

|

ADJDIR |

PHADJ |

LID[4:0] |

||||

|

3 |

SCR |

L[4:0] |

||||||

|

4 |

F[7:0] |

|||||||

|

5 |

|

K[4:0] |

||||||

|

6 |

M[7:0] |

|||||||

|

7 |

CS[1:0] |

N[4:0] |

||||||

|

8 |

SUBCLASS[2:0] |

N[4:0] |

||||||

|

9 |

JESDV[2:0] |

S[4:0] |

||||||

|

10 |

HD |

CF[4:0] |

||||||

|

11 |

RESERVED 1 |

|||||||

|

12 |

RESERVED 2 |

|||||||

|

13 |

FCHK[7:0] |

|||||||

Фаза данных с разрешенной заменой символа

В фазе передачи данных выравнивание кадра контролируется управляющими символами. Замена символов используется в конце фрейма. На этапе передачи данных не требуется никаких дополнительных действий для размещения данных или выравнивания фреймов. Замена символов позволяет вывести символ выравнивания на границе фрейма тогда и только тогда, когда последний символ текущего фрейма может быть заменен последним символом последнего фрейма, что облегчает (случайное) подтверждение того, что выравнивание не изменилось со времени выполнения последовательности ILAS (рис. 8, 9).

Замена символов в передатчике происходит в следующих случаях:

- если скремблирование отключено и последний октет кадра или мультикадра равен значению октета предыдущего кадра;

- если включено скремблирование и последний октет мультикадра равен 0x7C или последний октет кадра равен 0xFC.

В каждом из передатчиков и приемников работает локальный счетчик мультифреймов (LMFC), который постоянно считает до значения (F×K) – 1, а затем сбрасывается в «0» для повтора счета с начала (игнорируя внутреннюю ширину слова). Общий сигнал (подключенный к общему источнику) SYSREF выдается всем передатчикам и приемникам, по нему они сбрасывают локальные счетчики LMFC, в результате чего все LMFC должны быть синхронизированы (в течение одного такта) между собой.

Когда опускается сигнал SYNC (видимый всеми устройствами), передатчик запускает фазу ILAS при следующем (Tx) сбросе LMFC до «0». Если F×K был правильно установлен, чтобы быть больше, чем (время кодирования передачи) + (время распространения по сигнальной линии) + (время декодирования приемника), принятые данные будут переданы из SERDES приемника до начала следующего счета LMFC. Приемник передаст данные в FIFO, что позволит начать вывод данных на следующей (Rx) границе LMFC. Эта известное временное соотношение между входом SERDES передатчика и выходом FIFO приемника известна как детерминированная задержка.

Что может пойти не так?

JESD204B является сложным стандартом интерфейса, и в его работе имеется множество тонкостей. Чтобы выяснить, что не работает, требуется хорошее понимание вероятных сценариев.

Не удается выйти из фазы CGS: если SYNC остается на низком логическом уровне или импульсы для <4 мультикадров на высоком логическом уровне

Необходимо проверить плату без подачи питания:

- Сигналы SYSREF и SYNC~ должны «прозваниваться».

- При отключенной плате убедитесь, что линия сигнала SYNC~ от источника (на FPGA или DAC) до входа (на АЦП или FPGA) исправна и имеет низкий импеданс.

- Убедитесь, что подтягивающие к 0 или 1 резисторы не перетягивают сигнал слишком сильно, если, например, значение сопротивления слишком низкое или сигнал закорочен на питание или «землю», и, следовательно, неправильно управляется.

- Убедитесь, что разводка дифференциальных пар (и кабелей, если используются) линии JESD204B совпадает и выровнена.

- Убедитесь, что дифференциальное сопротивление линий на плате составляет 100 Ом.

Проверка платы после подачи питания:

- Если в цепи SYNC есть буфер / транслятор, убедитесь, что он работает правильно.

- Убедитесь, что линия на плате от источника сигнала SYNC~ до приемника (как SYNC+, так и SYNC–, если сигнал дифференциальный) рассчитана правильно, таким образом, что обеспечиваются логические уровни, совместимые с устройством, которое принимает сигнал SYNC~. Если логический уровень не соответствует, проверьте разводку сигнала от источника к приемнику и, чтобы найти проблему. Если параметры линии не соответствуют требованиям, обратитесь к изготовителю платы.

- Убедитесь, что передатчик JESD204B правильно настроен, и линия передачи данных правильно разведена, так что формируются правильные логические уровни для приемника данных JESD204B. Если логический уровень не соответствует требованиям, проверьте, как сконфигурированы схемы подключения источника и приемника, чтобы найти проблему. Если параметры линии не соответствуют требованиям, обратитесь к изготовителю платы.

Проверка сигнала SYNC~:

- Если SYNC~ имеет низкий логический уровень и не меняет состояние, соединение не продвигается дальше фазы CGS. Существует либо проблема с отправляемыми данными, либо приемник JESD204B неправильно декодирует выборку. Убедитесь, что символы K отправляются, проверьте параметры конфигурации приема, проверьте источник SYNC~, проверьте схему платы и попробуйте перегрузить сигнал SYNC~ , чтобы попытаться принудительно перевести соединение в фазу ILAS, и выявить отдельно — возникает ли эта проблема на стороне канала приемника или передатчика.

- Если SYNC~ имеет высокий логический уровень и не меняет состояние, убедитесь, что логический уровень SYNC~ правильно настроен на устройстве-источнике. Проверьте подтягивающие к 0 и 1 резисторы.

- Если SYNC~ импульсами устанавливается в высокий уровень, но сбрасывается в лог. 0 менее чем на шесть периодов мультифрейма, это значит, что соединение JESD204B выходит за пределы фазы CGS, но не выходит за пределы фазы ILAS. Это говорит о том, что символы /K/ в порядке, и основная функция CDR работает. Перейдите к разделу устранения неполадок ILAS.

- Если SYNC~ имеет импульсы с высокой длительностью более шести мультифреймовых периодов, связь выходит за пределы фазы ILAS и работает со сбоями в фазе данных (раздел фазы данных для рекомендаций по устранению неполадок).

Проверка передачи последовательных данных:

- Убедитесь, что передатчик и приемник настроены на одну скорость передачи данных.

- Измерьте линии с помощью щупа с высоким импедансом (дифференциальным, если это возможно); если символы отображаются неверно, убедитесь, что дифференциальные линии дорожек на плате совпадают, путь возвратного тока по опорному слою не прерывается и устройства правильно запаяны на печатной плате. В отличие от (как может показаться) случайных символов фазы ILAS и фазы данных, символы CGS легко распознаются на осциллографе или анализаторе (если доступен осциллограф с достаточно высокой скоростью).

- Проверьте K-символы на осциллографе со щупом с высоким сопротивлением:

- если символы верны, со стороны передатчика все работает правильно;

- если символы K неверные, скорее всего, возникла проблема с передатчиком или с физической передачей сигнала по дорожкам на плате.

- Если есть постоянный уровень напряжения, убедитесь, что синфазное напряжение передатчика и приемника соответствует тому, что в документации на устройства:

- в зависимости от реализации синфазное напряжение передатчика может варьироваться в пределах 490–1135 мВ;

- в зависимости от реализации синфазное напряжение приемника может варьироваться в пределах 490–1300 мВ.

- Проверьте дифференциальное напряжение CML-передатчика на линиях данных (обратите внимание, что дифференциальное напряжение CML рассчитывается как двукратное отклонение напряжения от каждого плеча сигнала).

- дифференциальное напряжение передатчика CML может варьироваться в пределах 0,5–1 В (п-п) для скоростей до 3,125 Гбит/с;

- дифференциальное напряжение передатчика CML может варьироваться в пределах 0,4–0,75 В (п-п) для скоростей до 6,374 Гбит/с;

- дифференциальное напряжение передатчика CML может варьироваться в пределах 0,36–0,77 В (п-п) для скоростей до 12,5 Гбит/с.

- Если есть возможность электроконтроля и контроля импеданса платы, включите и проверьте сигналы данных вдоль всего канала передачи данных.

- Убедитесь, что значения M и L совпадают у передатчика и приемника, в противном случае могут не совпадать скорости передачи данных. Например, M = 2 и L = 2 означают половину скорости передачи данных по последовательному интерфейсу по сравнению со случаем M = 2 и L = 1.

- Убедитесь, что тактовые сигналы, идущие к передатчику и приемнику, синхронизированы по фазе и имеют правильную частоту.

Невозможно завершить фазу ILAS, если SYNC выставляет высокие импульсы примерно на четыре мультифрейма

Конфликт параметров линии данных:

- Убедитесь, что параметры канала не смещены на 1 (значение многих параметров указано как -1).

- Убедитесь, что мультифреймы ILAS передаются должным образом, проверьте параметры линии на приемопередающем устройстве, приемном устройстве и параметры, передаваемые во втором мультифрейме ILAS.

- Рассчитайте нужную длину ILAS (tframe, tmultiframe, 4×tmultiframe), убедитесь, что ILAS принимается приблизительно для четырех мультикадров.

- Убедитесь, что все линии работают нормально. Убедитесь, что нет конфликтов между каналами и линиями данных разных устройств.

- Убедитесь, что все линии работают нормально. Убедитесь, что нет конфликтов между каналами и линиями данных разных устройств.

Происходит переход в фазу данных, но иногда сбрасывается связь (возвращается к CGS и ILAS, прежде чем вернуться к фазе данных)

Возможные причины:

- Неверная настройка времени установки и удержания периодического или периодически прерываемого сигнала SYSREF или SYNC~.

- Конфликт параметров линии связи.

- Конфликты замены символа

- Проблема скремблирования, если оно включено

- Повреждение, шум или джиттер на линии данных приводящее к закрытию глазковой диаграммы.

- Ложное тактирование или высокий джиттер тактового сигнала устройства.

Другие общие советы по устранению неполадок:

- Запустите преобразователь и канал на самой низкой поддерживаемой скорости, это позволит использовать более доступные измерительные инструменты с более низкой пропускной способностью.

- Установите минимально допустимые комбинации M, L, K, S.

- Используйте тестовые режимы, когда это возможно.

- Используйте подкласс 0 для устранения неполадок.

- Отключайте скремблирование при устранении неполадок

Это руководство по устранению неполадок не претендует на то, чтобы быть всеобъемлющим, но предоставляет хорошую базовую основу для инженера, работающего и желающего узнать о работе JESD204B.

Краткое изложение спецификации JESD204B содержит практическую информацию о линии передачи данных. Надеемся, что инженеры, ознакомившиеся с этим новейшим стандартом высокопроизводительного интерфейса, найдут его информативным и полезным, если потребуется устранение решение проблем в процессе разработки.

Синхронизация нескольких АЦП/ЦАП с интерфейсом JESD

В большинстве случаев в системах связи, в приборостроении, в системах сбора сигналов требуется наличие возможности одновременно собирать входные аналоговые сигналы с нескольких аналого-цифровых преобразователей (АЦП). Затем полученные данные должны быть обработаны с учетом возможностей по синхронизации аналоговых входов, которые имеют свои собственные задержки. Исторически для разработчиков, которые использовали АЦП с LVDS и с параллельным выходом, это было достаточно трудной задачей.

JESD204B представляет собой интерфейс высокоскоростной последовательной передачи данных по одной или нескольким дифференциальным парам сигналов, например для выходов АЦП. В соответствии со спецификацией интерфейс JESD204B имеет встроенную схему для грубого выравнивания по линиям. Данные разбиты на отдельные фреймы, которые непрерывно отправляются получателю. Подкласс 1 интерфейса JESD204B обеспечивает выравнивание данных на уровне выборок по нескольким последовательным каналам данных или нескольких АЦП с использованием опорных сигналов системных событий (SYSREF) для синхронизации тактирования фреймов в передатчике и приемнике. Это дает детерминированную задержку для устройств, работающих по каналу JESD204B. Однако по-прежнему существует много проблем, которые разработчик должен преодолеть для достижения полной синхронизации выборок — это разводка печатной платы, согласование сигналов тактирования и правильная генерация сигнала SYSREF в соответствии таймингами, периодичностью SYSREF и задержками цифрового FIFO

Разработчик должен сразу понимать, как будут подключены и распределены по системе тактовые сигналы и сигнал SYSREF. В идеале тактовый сигнал и SYSREF должны иметь одинаковый уровень и смещение, чтобы предотвратить внутренний перекос на входе микросхемы. Частота обновления состояния сигнала SYSREF должна быть определена либо как одиночное событие при запуске, либо как повторяющийся сигнал, который может появиться в любое время, когда требуется синхронизация. По умолчанию считаем, что мы имеем максимальный разбег сигнала SYSREF и тактового сигнала, поэтому необходима тщательная разводка печатной платы, которая будет соответствовать требованиям к таймингу для соединений на плате, для разъемов и объединительных плат и различных компонентов. Наконец, дизайн цифрового FIFO и сигналы, проходящие через несколько тактовых доменов, создают собственный перекос цифрового буфера в передатчиках и приемниках JESD204B, который должен учитываться и удаляться при обработке внутренних данных.

Тактирование системы может быть реализовано от разных источников, таких как кварцевые резонаторы, VCO, микросхемы-генераторы тактовых импульсов. Параметры тактирования определяются производительностью системы: при необходимости синхронизации нескольких АЦП, сигнал SYSREF должен быть синхронизирован с входным тактовым сигналом. Это диктует более высокие требования к выбору источника тактирования — необходимо, чтобы фронт SYSREF четко совпадал с известным фронтом тактового сигнала в определенный момент времени. Если сигнал SYSREF и тактовый сигнал не синхронизированы по фазе, этого не удастся достичь.

ПЛИС может также быть источником события SYSREF. Однако если ПЛИС не синхронизируется с тактовой частотой основной выборки, которая отправляется на АЦП, будет сложно синхронизировать с ним по фазе сигнал SYSREF от ПЛИС. Альтернативный подход состоит в том, чтобы предоставить сигнал SYSREF от микросхемы генерации или распределения тактирования, которая может синхронизировать этот сигнал по фазе с несколькими тактовыми сигналами, которые отправляются по всей системе. При использовании такого метода событие SYSREF может быть одноразовым событием при запуске или повторяющимся сигналом в зависимости от требований к системе.

Пока детерминированная задержка остается постоянной в системе между АЦП и ПЛИС, дополнительные импульсы SYSREF могут не потребоваться, кроме как для помощи в формировании определенных системных данных. Следовательно, периодический импульс SYSREF для выравнивания тактовой частоты можно игнорировать или фильтровать до момента потери синхронизации. В качестве альтернативы импульс SYSREF может быть обработан без сброса линка JESD204B.

Для того чтобы обозначить детерминированную начальную точку старта работы каналов АЦП (рис. 10), разработчик должен иметь возможность выдерживать правильные временные характеристики распространения импульса SYSREF по системе. Это означает, что ожидаемое время установки и удержания относительно тактового сигнала должно соблюдаться без нарушений. Использование относительно длинного импульса SYSREF, продолжающегося в течение нескольких тактовых циклов, может быть подходящим решением для удовлетворения требований времени удержания при условии, что также будет соблюдено время установки первого необходимого тактового сигнала. Для обеспечения минимального перекоса тактовых импульсов и SYSREF понадобится согласование длины дорожек, а следовательно, пристальное внимание к разводке печатной платы. Это может быть наиболее сложной частью достижения синхронной обработки выборки по каналам.

AD9250 (рис. 10) — это 14-разрядный сдвоенный АЦП со скоростью 250 MSPS от Analog Devices, который поддерживает интерфейс JESD204B в реализации подкласса 1. Этот подкласс обеспечивает синхронизацию аналоговой выборки между АЦП с помощью сигнала события SYSREF. AD9525 (рис. 10) — генератор тактовых импульсов с низким уровнем джиттера, который не только обеспечивает семь выходов тактовой частоты до 3,1 ГГц, но и синхронизирует выходной сигнал SYSREF в зависимости от пользовательской конфигурации. Оба продукта в сочетании с набором продуктов с разветвленным буфером от Analog Devices обеспечивают основу для точной синхронизации и согласования нескольких данных АЦП, обрабатываемых на FPGA или ASIC.

- JEDEC Standard JESD204 (April 2006). JEDEC Solid State Technology

- JEDEC Standard JESD204A (April 2008). JEDEC Solid State Technology

- JEDEC Standard JESD204B (July 2011). JEDEC Solid State Technology Association

- jedec.org/sites/default/files/docs/JESD204C.pdf

- analog.com/en/analog-dialogue/articles/jesd204c-primer-part1.html

- Harris J. What Is JESD204 and Why Should We Pay Attention to It?

- Beavers I. Synchronizing Multiple ADCs Using JESD204B.

- DeSimone A., Giancioppo M. Grasp the Critical Issues for a Functioning JESD204B Interface.

- Diniz G. JESD204B vs. Serial LVDS Interface Considerations for Wideband Data Converter Applications.

отправка...

отправка...

21 марта, 2011

21 марта, 2011