Комплексный подход к освоению интерфейсов ARINC‑429 и МКИО

Виды и уровни электрических сигналов интерфейсов в комплексах, системах и функционально независимых устройствах оборудования самолетов, вертолетов и сопрягаемых с ними узлов регламентируются ГОСТ 18977, РТМ 1495 (ARINC‑429), ГОСТ Р 52070 (MIL STD 1553b).

Требования к интерфейсу двуполярного последовательного кода (ДПК) изложены в ГОСТ 18977 и РТМ 1495 (ARINC‑429), а в ГОСТ Р 52070 (MIL STD 1553b) — к интерфейсу мультиплексного канала информационного обмена (МКИО).

Типовые структурные схемы технических средств для организации этих интерфейсов приведены на рис. 1 и 2 [1, 2].

Рис. 2. Структурная схема технических средств интерфейса МКИО:

1 — магистральная шина;

2 — резервная магистральная шина;

3 — ответвитель;

4 — резервный ответвитель

В таблице 1 приведены основные технические характеристики интерфейсов ARINC‑429 и МКИО.

|

Характеристика |

ГОСТ 18977 и РТМ 1495 |

ГОСТ Р 52070 |

|---|---|---|

|

Аналог |

ARINC-429 |

MIL-STD-1553b |

|

Скорость передачи, кбит/с |

12,5, 50, 100, 250, 500, 1000 |

1000 |

|

Кодирование |

Самосинхронизирующийся RZ-код данных |

Биполярный фазоманипулированный код Манчестер-2 |

|

Уровни сигналов в линии связи |

+10±3 В — «1» кода –10±3 В — «0» кода 0±0,5 В — пауза для передатчика 0±2,5 В — пауза для приемника |

Размах от 6 до 9 В |

|

Размер слова, бит |

32 |

32 |

|

Максимальное количество |

20 |

31 |

|

Тип линии связи |

Несогласованная витая пара |

Согласованная витая пара |

|

Трансформаторная развязка |

По стандарту не предусмотрена |

Обязательна |

|

Способ связи |

Симплекс или полудуплекс |

Полудуплекс |

|

Принцип передачи |

Широковещательный |

Команда-ответ, широковещательный |

|

Принцип приема |

Тип информации (адрес) в каждом слове |

Адрес абонента и тип информации |

|

Сфера применения |

Авионика |

Авионика |

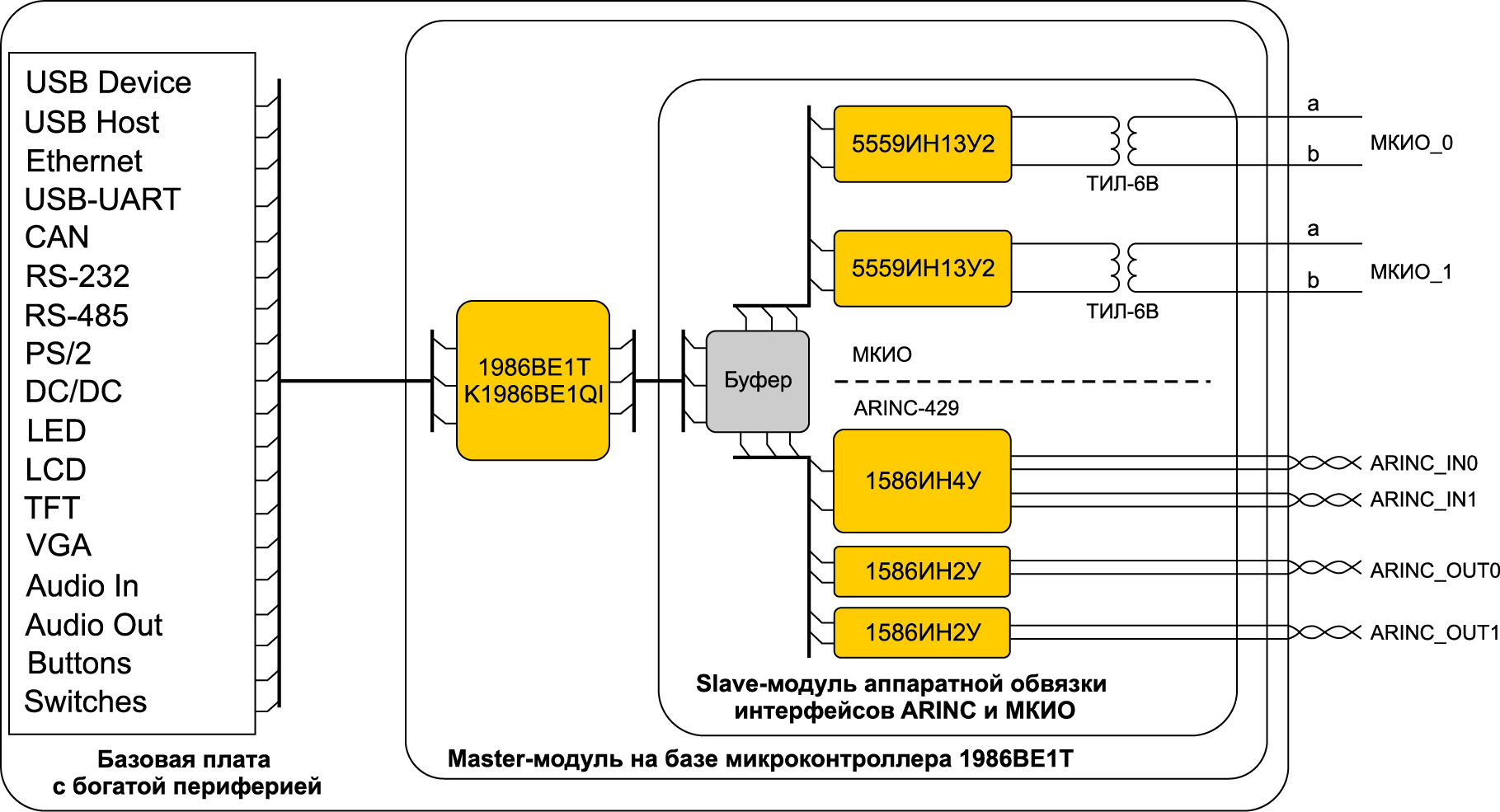

Разрабатывая программно-аппаратный комплекс, в котором необходимо использовать линии передачи данных ARINC‑429 и МКИО, следует решить вопрос организации протокольной и аппаратной части интерфейса. При этом желательно опереться на чей-то опыт и применить уже имеющиеся наработки в виде законченного узла, способного выполнить задачу конечного устройства. Идеальным решением может стать отладочный комплекс, для которого понадобится написать и отладить программное обеспечение (рис. 3).

Рис. 3. Блок-схема программно-аппаратного отладочного комплекса для организации интерфейса ARINC 429 и МКИО

В целях сокращения сроков разработки и уменьшения количества ошибок при решении данной задачи желательно применить интегральную микросхему, в которой реализована протокольная часть интерфейса ARINC‑429 и МКИО.

Протокольная часть отладочного комплекса

Решением данной задачи может стать применение микроконтроллера фирмы АО «ПКК Миландр» 1986ВЕ1T в металлокерамическом корпусе 4229.132-3 или K1986BE1QI в легком пластиковом корпусе LQFP‑144 (рис. 4). Микроконтроллер 1986ВЕ1Т включен в «Перечень электронной компонентной базы, разрешенной для применения при разработке, модернизации, производстве и эксплуатации вооружения, военной и специальной техники». Основные технические характеристики приведены в таблице 2 [3].

|

Характеристика |

Значение |

|---|---|

|

Ядро |

32-битное RISC-ядро |

|

Тактовая частота |

144 МГц |

|

Производительность |

0,8 DMIPS/МГц при нулевой задержке памяти |

|

FLASH-память программ |

128 кбайт |

|

ОЗУ |

48 кбайт |

|

Контроллер внешней шины |

СОЗУ, ПЗУ, NAND Flash |

|

Питание |

Внешнее питание 3–3,6 В Встроенный регулятор напряжения на 1,8 В для питания ядра |

|

Умножитель PLL |

PLL для ядра; PLL для USB |

|

Часы реального времени |

Встроенный домен |

|

АЦП |

12-разрядный АЦП (до 8 каналов) |

|

ЦАП |

12-разрядный ЦАП (до 2 каналов) |

|

ШИМ |

32-разрядный ШИМ (до 16 каналов) |

|

Интерфейсы |

2×CAN, 2×UART, 3×SPI, Ethernet 10/100 и PHY Transceiver, USB Device и Host |

|

Интерфейсы программирования |

SWD, JTAG, UART-загрузчик |

|

Интерфейсы отладки |

SWD, JTAG |

|

Линии ввода / вывода |

96 |

|

Интерфейс по ГОСТ 18977-79 (ARINC-429) |

1 |

|

Интерфейс по ГОСТ Р 52070-2003 (МКИО) |

2 |

Особенностью микроконтроллера 1986ВЕ1T является не только наличие интерфейсов ГОСТ 18977-79 (ARINC‑429) и ГОСТ Р 52070-2003 (МКИО), но и встроенный цифровой контроллер интерфейса Ethernet 10/100 и PHY Transceiver, что упрощает организацию схемотехнической развязки линий Ethernet.

Выводы контроллера могут быть переопределены на дополнительные функции с выводом интерфейсных линий ARINC‑429 и МКИО, требующих дополнительной аппаратной обвязки с применением специальных приемопередатчиков.

Аппаратная часть отладочного комплекса

Решить задачу работы с аналоговой частью авиационных интерфейсов можно, применив микросхемы производства ОАО «НПО «Физика» (рис. 5):

- приемопередатчики МКИО 5559ИН13У2;

- передатчики двуполярного последовательного кода 1586ИН2У;

- одноканальные и двухканальные приемники двуполярного последовательного кода 1586ИН3У, 1586ИН4У.

Данные микросхемы при напряжении питания +5 (±5 В для передатчика ДПК 1586ИН2У) имеют входы с уровнем логической единицы от 2,5 В, что позволяет стыковать их напрямую с микроконтроллерами и ПЛИС, разработанными на напряжение питания 3,3 В [5].

Микросхемы приемников и передатчиков по ГОСТ 18977

Интерфейс цифровой части микросхем приемников и передатчиков ДПК 1586ИН2У, 1586ИН3У, 1586ИН4У дублирует интерфейс известных микросборок типа 75АП001, АП003, АП004 и их аналогов Ф001, Ф003, Ф004 А, выпускаемых ОАО «НПО «Физика». В этом интерфейсе используются три линии управления: линия синхронизации (SYN), информационная (INF), а также линия разрешения работы (CON) [6]. На рис. 6 приведена осциллограмма работы микросхемы 1586ИН2У, на которой представлены три линии управления и один из выходных сигналов Ya.

Идентичность интерфейсов микросборок 75АП001, АП003, АП004 с интерфейсом микросхем 1586ИН2У, 1586ИН3У, 1586ИН4У позволяет осуществлять замену микросборок серии АП00х на микросхемы серии 1586 в аппаратуре заказчика без проведения дополнительных работ по изменению цифровой части схемы. Такая замена может привести к существенной экономии средств, расходуемых на интерфейсные схемы, экономии места на печатной плате, уменьшению массы аппаратуры.

В то же время зарубежная фирма HOLT IC использует другой интерфейс цифровой части схемы приемников и передатчиков ДПК с двумя линиями управления. В целях импортозамещения ОАО «НПО «Физика» разработало микросхемы 1586ИН2АУ, 1586ИН4АУ с интерфейсом, аналогичным применяемым фирмой HOLT IC, и проводит работы по постановке данных микросхем на серийное производство. На рис. 7 приведена осциллограмма работы микросхемы 1586ИН2АУ, на которой показаны две линии управления — DA и DB и выходные сигналы Ya и Yb. Появление единицы на входе DA означает передачу «1» в линию, появление единицы на входе DB означает передачу «0» в линию, появление единиц на обеих линиях DA и DB — перевод выходов в Z‑состояние. Наличие Z‑состояния на выходе передатчика позволяет использовать линию связи в качестве общей (в соответствии с ГОСТ 18977 общая линия — это линия связи, к которой подключено два или более передающих устройств, причем информация различных передающих устройств, поступающая в линию, разнесена во времени).

Уменьшение количества входов управления у микросхемы передатчика 1586ИН2АУ позволило не использовать парные боковые выводы микросхемы [4]. Эти выводы могут быть удалены потребителем, что увеличивает плотность компоновки микросхем на плате.

В дальнейшем ОАО «НПО «Физика» планирует провести разработку микросхем передатчиков на однополярном питании — аналогов микросхемы HI‑8596.

Уровень стойкости к воздействию специального фактора «7.С» микросхем приемников и передатчиков ДПК серии 1586 с характеристикой 7.С4 составляет не менее 2,0·1УС.

Микросхемы приемопередатчиков по ГОСТ Р 52070

Микросхемы приемопередатчиков серии 5559ИН13, выпускаемые с 2007 года, являются оригинальной разработкой ОАО «НПО «Физика». Эта серия микросхем постоянно пополняется и совершенствуется в направлениях повышения стойкости к специальным воздействиям и сокращения энергопотребления (табл. 3).

|

Обозначение |

Тип |

Особенности |

|---|---|---|

|

5559ИН13Т |

4131.24-3 |

Предназначена для работы с большим трафиком, имеет входы настройки длительности фронта |

|

5559ИН13У |

Н09.28-1В |

Имеет входы настройки длительности фронта |

|

5559ИН13У1 |

Н04.16-1В |

Выполнена в меньшем корпусе 7,8×7,8 мм (выводы на 2 стороны) по сравнению с 5559ИН13У 9,4×9,4 мм. Данная особенность позволяет достигать более компактной топологии печатной платы устройства |

|

5559ИН13У2 |

Н04.16-1В |

По сравнению с 5559ИН13У1 имеет входы с уровнем логической единицы от 2,5 В |

На рис. 8 приведена осциллограмма работы микросхемы 5559ИН13У2.

Рис. 8. Осциллограмма работы микросхемы 5559ИН13У2 с трансформатором ТИЛ-6В:

канал 1 — передача;

каналы 2, 3 — прием

Микросхемы приемопередатчиков серии 5559ИН13 по ГОСТ Р 52070 характеризуются повышенной радиационной стойкостью:

Уровень стойкости к воздействию специальных факторов «7.С», «7.И» с характеристиками 7.С1, 7.И7, 7.С4 составляет не менее 60·1УС для 7.С1; 2·2УС для 7.И7; 1,8·1УС для 7.С4.

При испытаниях на воздействие тяжелых заряженных частиц с уровнем линейных потерь энергии не менее 40 МэВ·см2/мг одиночные эффекты или катастрофические отказы не зафиксированы.

Все микросхемы серии 5559ИН13 включены в «Перечень ЭКБ», передатчики 1586ИН2У заявлены на включение в «Перечень ЭКБ» (ред. 2015 года), включение приемников 1586ИН3У, 1586ИН4У в «Перечень ЭКБ» планируется в 2016 году.

Отладочный комплект HELPER

В целях облегчения освоения интерфейсов ARINC‑429 и МКИО по стандартам ГОСТ 18977-79 и ГОСТ Р 52070-2003 компанией LDM-SYSTEMS был разработан slave-модуль специализированного интерфейса LDM-HELPER-SI (рис. 9).

LDM-HELPER-SI позволяет выбирать один из двух интерфейсов ARINC‑429 или МКИО посредством двунаправленных буферов или переключателей.

Интерфейс МКИО аппаратно основан на двух микросхемах 5559ИН13У2 производства ОАО «НПО «Физика» и двух трансформаторов ТИЛ‑6В производства ОАО «Мстатор».

Интерфейс ARINC‑429 аппаратно основан на одной микросхеме 1586ИН4У (входные каналы) и двух микросхемах 1586ИН2У (выходные каналы) производства ОАО «НПО «Физика».

Линии ARINC‑429 или МКИО выведены на 15‑выводной PLS-разъем.

LDM-HELPER-SI входит в линейку большого отладочного комплекта семейства HELPER, особенностью которого является модульность, состоящего из трех групп:

- Main Board — это «Базовые платы», содержащие набор периферийных устройств ввода/вывода информации, устройств визуальной или аудиоиндикации, а также различных органов управления.

- Master-модули — это «Ведущие платы», содержащие программно-ориентированный компонент в виде микроконтроллеров, микропроцессоров или ПЛИС. Master-модули построены таким образом, что уже содержат все необходимые элементы для взаимодействия как с другими модулями, так и с простейшими устройствами ввода/вывода информации. Для ознакомления со спецификой работы установленного программно-ориентированного элемента наличие «Базовой платы» или каких-либо других модулей не является обязательным, они могут использоваться отдельно и встраиваться в разрабатываемые устройства в виде законченного узла.

- Slave-модули — это «Ведомые платы», содержащие элементы, в значительной мере расширяющие функциональность отладочного комплекта.

Помимо этого, важной особенностью HELPER является надежное механическое крепление составных частей отладочного комплекта, позволяющее без снижения надежности размещать вертикально множество модулей, получая таким образом функционально законченные конструкции самого различного назначения.

Наиболее полная структура комплекта HELPER, в целях освоения интерфейсов ARINC‑429 и МКИО, может включать в себя (рис. 10) [7, 8, 9]:

- базовую плату LDM-HELPER-MB501;

- Master-модуль LDM-HELPER-K1986BE1QI (K1986BE1QI или 1986BE1T);

- slave-модуль LDM-HELPER-SI.

На рис. 11 приведена фотография отладочного комплекта HELPER в сборе в полной комплектации.

В случае использования Master-модуля LDM-HELPER-K1986BE1QI с установленной микросхемой в металлокерамическом корпусе 1986BE1T (рис. 12), ввиду ее большой высоты, необходимо использовать дополнительные промежуточные вставки LDM-HELPER-CON, увеличивающие зазор между платами LDM-HELPER-K1986BE1QI и LDM-HELPER-SI.

Программирование и отладка кода ведется в программном обеспечении Keil или аналогах. Master-модуль LDM-HELPER-K1986BE1QI имеет встроенный USB-UART-загрузчик без режима отладки. В случае если режим отладки необходим, следует использовать программатор ULINK2 или аналоги.

В заключение данной статьи хотелось бы отметить, что отладочный комплект HELPER должен стать удобным помощником при освоении интерфейсов ARINC‑429 и МКИО по стандартам ГОСТ 18977-79 и ГОСТ Р 52070-2003.

- ГОСТ 18977-79. Комплексы бортового оборудования самолетов и вертолетов. Типы функциональных связей. Виды и уровни электрических сигналов.

- ГОСТ Р 52070-2003. Интерфейс магистральный последовательный системы электронных модулей. Общие требования.

- Спецификация ТСКЯ.431296.008CП 32‑разрядный контроллер для авиационного применения 1986ВЕ1Т, К1986ВЕ1Т, К1986ВЕ1ТК, К1986ВЕ1QI, К1986ВЕ1Н4.

- Техническое описание на микросхему 1586ИН2АУ.

- Техническое описание на микросхему 1586ИН2У.

- Техническое описание на микросхемы 1586ИН3У, 4У.

- Руководство по эксплуатации LDM-HELPER-SI.

- Руководство по эксплуатации LDM-HELPER-K1986BE1QI.

- Руководство по эксплуатации LDM-HELPER-MB501.

отправка...

отправка...

14 марта, 2021

14 марта, 2021